MSK050C-0300-NN-S1-BG0-NNNN

GCSR允许VMEbus主机重置本地总线。

此功能非常危险,应与一起使用

小心本地重置功能是部分系统重置,而不是

完整的系统重置,如通电重置或

SYSRESET*。当本地总线复位信号被断言时

本地总线循环可能中止。VMEchip2已连接

连接到本地总线和VMEbus,如果

VMEbus的循环是有界的,可能会导致不稳定的操作。

本地处理器与a之间的通信

VMEbus主机应使用中断或邮箱位置;

正常通信中不应使用重置。重置

应仅在本地处理器停止时使用,或

本地总线挂起,重置是后的手段。

当MVME162处于重置状态时,任何VMEbus对其的访问将被忽略。如果

启用全局总线定时器时,会生成总线错误。

操作说明

3-26用户手册

3.

MVME162/D24-1

4.功能性

描述

介绍

本章描述了块上的MVME162嵌入式控制器

图级。功能描述概述了

MVME162,随后详细描述了MVME162

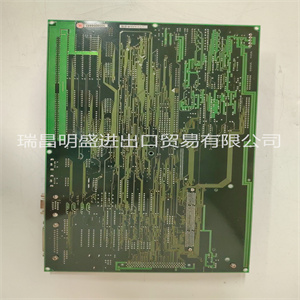

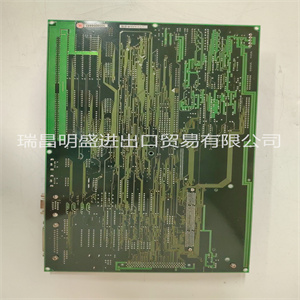

电路。图4-1显示了MVME162主模块的框图。

图4-2显示了奇偶性DRAM夹层模块的框图。

其他MVME162块的说明,包括中的可编程寄存器

嵌入式MVME162中给出了ASIC和外围芯片

控制器程序员参考指南。有关功能的其余部分,请参阅

MVME162的描述。

MVME162功能描述

MVME162是一种高功能VMEbus单板计算机

围绕MC68040/MC68LC040芯片设计。它有1MB、4MB或8MB的

DRAM、512KB SRAM、1MB闪存、四MVIP工业封装

接口和两个串行端口(一个EIA-232-D DCE;一个EIA232-D或EIA530 DCE/DTE)。选项包括SCSI大容量存储接口、LAN

以太网收发器接口和非VMEbus版本。

数据总线结构

MVME162上的本地数据总线是32位同步总线,基于

在MC68040总线上,支持突发传输和监听。这个

各种本地总线主设备和从设备使用本地总线进行通信。

本地总线由优先级类型仲裁器和本地总线的优先级进行仲裁

总线主控从高到低依次为:82596CA LAN、NCR 53C710 SCSI,

VMEbus和MPU。一般来说,任何主设备都可以访问任何从设备;

然而,并非所有组合都能通过常识测试。参考

MVME162嵌入式控制器程序员参考指南

每个设备确定其端口大小、数据总线连接和任何

访问设备时应用的限制。

功能描述

4-2用户手册

4.

MC68040/MC68LC040微处理器

MVME162配备MC68040或MC68LC040微处理器。

MC68040/MC68LC040具有片上指令和数据缓存;这个

MC68040还提供浮点协处理器。请参阅M68040

有关更多信息,请参阅微处理器用户手册。

EPROM和闪存

MVME162实现包括四个组织的2-Mbit闪存设备

在256Kbit x 8配置中。EPROM位置是标准的JEDEC 32-

引脚PLCC能够实现4Mbit密度(128kbit x 8;256kbit x 7;512kbit x 8;

1Mbit x8)组织为512Kbit x 8设备。跳线设置(GPIO3,引脚9-

J22上的10)允许从闪存(GPIO3)获取重置代码

安装的)或从EPROM(GPIO3被移除)。

SRAM

MVME162在单个系统中提供512KB 32位宽的板载静态RAM

非交错架构,带车载电池备份。坏的情况

电池保护的运行时间为200天。SRAM的细节

性能可在中的SRAM内存控制器部分中找到

中的MCchip编程模型

MSK050C-0300-NN-S1-BG0-NNNN

MSK050C-0300-NN-S1-BG0-NNNN

The GCSR allows a VMEbus master to reset the local bus.

This feature is very dangerous and should be used with

caution. The local reset feature is a partial system reset, not

a complete system reset such as powerup reset or

SYSRESET*. When the local bus reset signal is asserted, a

local bus cycle may be aborted. The VMEchip2 is connected

to both the local bus and the VMEbus and if the aborted

cycle is bound for the VMEbus, erratic operation may result.

Communications between the local processor and a

VMEbus master should use interrupts or mailbox locations;

reset should not be used in normal communications. Reset

should be used only when the local processor is halted or

the local bus is hung and reset is the last resort.

Any VMEbus access to the MVME162 while it is in the reset state is ignored. If

a global bus timer is enabled, a bus error is generated.

Operating Instructions

3-26 User’s Manual

3

MVME162/D24-1

4 FUNCTIONAL

DESCRIPTION

Introduction

This chapter describes the MVME162 Embedded Controller on a block

diagram level. The Functional Description provides an overview of the

MVME162, followed by a detailed description of several blocks of MVME162

circuitry. Figure 4-1 shows a block diagram of the MVME162 main module.

Figure 4-2 shows a block diagram of the parity DRAM mezzanine module.

Descriptions of other MVME162 blocks, including programmable registers in

the ASICs and peripheral chips, are given in the MVME162 Embedded

Controller Programmer’s Reference Guide. Refer to it for the rest of the functional

description of the MVME162.

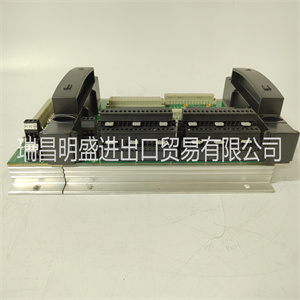

MVME162 Functional Description

The MVME162 is a high-functionality VMEbus single board computer

designed around the MC68040/MC68LC040 chip. It has 1MB, 4MB, or 8MB of

DRAM, 512KB of SRAM, 1MB Flash memory, four MVIP IndustryPack

interfaces, and two serial ports (one EIA-232-D DCE; one EIA-232-D or EIA530 DCE/DTE). Options include an SCSI mass storage interface, a LAN

Ethernet transceiver interface, and a non-VMEbus version.

Data Bus Structure

The local data bus on the MVME162 is a 32-bit synchronous bus that is based

on the MC68040 bus, and which supports burst transfers and snooping. The

various local bus master and slave devices use the local bus to communicate.

The local bus is arbitrated by priority type arbiter and the priority of the local

bus masters from highest to lowest is: 82596CA LAN, NCR 53C710 SCSI,

VMEbus, and MPU. Generally speaking, any master can access any slave;

however, not all combinations pass the common sense test. Refer to the

MVME162 Embedded Controller Programmer’s Reference Guide and to the user’s

guide for each device to determine its port size, data bus connection, and any

restrictions that apply when accessing the device.

Functional Description

4-2 User’s Manual

4

MC68040/MC68LC040 MPU

The MVME162 is equipped with an MC68040 or MC68LC040 microprocessor.

The MC68040/MC68LC040 have on-chip instruction and data caches; the

MC68040 also provides a floating-point coprocessor. Refer to the M68040

Microprocessor User’s Manual for more information.

EPROM and Flash Memory

The MVME162 implementation includes four 2-Mbit Flash devices organized

in a 256Kbit x 8 configuration. The EPROM location is a standard JEDEC 32-

pin PLCC capable of 4 Mbit densities (128 Kbit x 8; 256 Kbit X 8; 512 Kbit x 8;

1 Mbit x8) organized as a 512Kbit x 8 device. A jumper setting (GPIO3, pins 9-

10 on J22) allows reset code to be fetched either from Flash memory (GPIO3

installed) or from the EPROM (GPIO3 removed).

SRAM

The MVME162 provides 512KB of 32-bit-wide onboard static RAM in a single

non-interleaved architecture with onboard battery backup. The worst case

elapsed time for battery protection is 200 days. Specifics on SRAM

performance can be found in the section on the SRAM Memory Controller in

the MCchip Programming Model in

Copyright ©2019-2022 瑞昌明盛自动化设备有限公司 版权所有 赣ICP备2021006016号